Introduction to the PC busses

The PC receives and sends its data from and to busses. They can be divided into:

l The system bus, which connects the CPU with RAM

l I/O busses, which connect the CPU with other components.

The point is, that the system bus is the central bus. Actually, it connects to the I/O busses, as

An illustrated Guide to the PC System BUS

Introduction to the PC busses

The PC receives and sends its data from and to busses. They can be divided into:

l The system bus, which connects the CPU with RAM

l I/O busses, which connect the CPU with other components.

The point is, that the system bus is the central bus. Actually, it connects to the I/O busses, as

An illustrated Guide to the PC System BUS

file:///E|/education/Click & Learn/module2b.htm (3 of 8) [4/15/1999 6:17:39 AM]

you can see in this illustration:

You see the central system bus, which connects the CPU with RAM. A bridge connects the I/O

busses with the system bus and on to RAM. The bridge is part of the PC chip set, which will be

covered in module 2c.

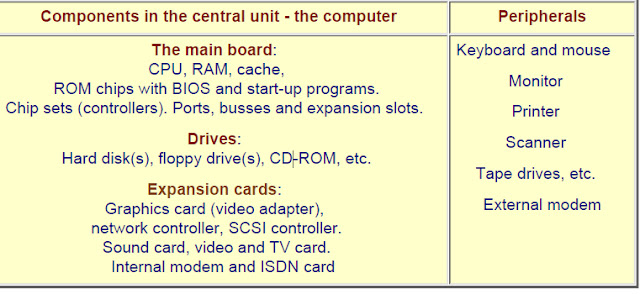

3 different I/O busses

The I/O busses move data. They connect all I/O devices with the CPU and RAM. I/O devices are

those components, which can receive or send data (disk drives, monitor, keyboard, etc. ). In a

modern Pentium driven PC, there are two or three different I/O busses:

l The ISA bus, which is oldest, simplest, and slowest bus.

l The PCI bus, which is the fastest and most powerful bus.

l The USB bus, which is the newest bus. It may in the long run replace the ISA bus.

The three I/O busses will be described later. Here, we will take a closer look at the PC's

fundamental bus, which the others are branches from:

The system bus

The system bus connects the CPU with RAM and maybe a buffer memory (L2-cache). The

An illustrated Guide to the PC System BUS

system bus is the central bus. Other busses branch off from it.

The system bus is on the system board. It is designed to match a specific type of CPU.

Processor technology determines dimensioning of the system bus. At the same time, it has taken

much technological development to speed up "traffic" on the system board. The faster the

system bus gets, the faster the remainder of the electronic components must be..

The following three tables show different CPU's and their system busses:

We see, that system bus speed follows the CPU's speed limitation. First at the fourth generation

CPU 80486DX2-50 are doubled clock speeds utilized. That gives the CPU a higher internal clock

frequency. The external clock frequency, used in the system bus, is only half of the internal

frequency

66 MHz bus

The PC receives and sends its data from and to busses. They can be divided into:

l The system bus, which connects the CPU with RAM

l I/O busses, which connect the CPU with other components.

The point is, that the system bus is the central bus. Actually, it connects to the I/O busses, as

An illustrated Guide to the PC System BUS

Introduction to the PC busses

The PC receives and sends its data from and to busses. They can be divided into:

l The system bus, which connects the CPU with RAM

l I/O busses, which connect the CPU with other components.

The point is, that the system bus is the central bus. Actually, it connects to the I/O busses, as

An illustrated Guide to the PC System BUS

file:///E|/education/Click & Learn/module2b.htm (3 of 8) [4/15/1999 6:17:39 AM]

you can see in this illustration:

You see the central system bus, which connects the CPU with RAM. A bridge connects the I/O

busses with the system bus and on to RAM. The bridge is part of the PC chip set, which will be

covered in module 2c.

3 different I/O busses

The I/O busses move data. They connect all I/O devices with the CPU and RAM. I/O devices are

those components, which can receive or send data (disk drives, monitor, keyboard, etc. ). In a

modern Pentium driven PC, there are two or three different I/O busses:

l The ISA bus, which is oldest, simplest, and slowest bus.

l The PCI bus, which is the fastest and most powerful bus.

l The USB bus, which is the newest bus. It may in the long run replace the ISA bus.

The three I/O busses will be described later. Here, we will take a closer look at the PC's

fundamental bus, which the others are branches from:

The system bus

The system bus connects the CPU with RAM and maybe a buffer memory (L2-cache). The

An illustrated Guide to the PC System BUS

system bus is the central bus. Other busses branch off from it.

The system bus is on the system board. It is designed to match a specific type of CPU.

Processor technology determines dimensioning of the system bus. At the same time, it has taken

much technological development to speed up "traffic" on the system board. The faster the

system bus gets, the faster the remainder of the electronic components must be..

The following three tables show different CPU's and their system busses:

We see, that system bus speed follows the CPU's speed limitation. First at the fourth generation

CPU 80486DX2-50 are doubled clock speeds utilized. That gives the CPU a higher internal clock

frequency. The external clock frequency, used in the system bus, is only half of the internal

frequency

66 MHz bus

.jpg)