Hardware Interrupts

The adapter or unit on the I/O bus uses the interrupt to signal request to send or receive data. An interrupt

signal is like a door bell. The unit signals by applying a voltage to one of the wires in the bus - an IRQ.

When the CPU acknowledges the signal, it knows that the unit wants send or receive data, or is finished.

The advantage of IRQ's is that the CPU can manage other tasks, while an adapter "massages" its data.

When the adapter has finished its task, it will report to the CPU with a new IRQ.

As an example, let us see how keyboard data are handled. The keyboard send bits, serially, through the

cable to the keyboard controller. The controller organizes them in groups of 8 (one byte). Every time it has a

byte, it sends an IRQ to the I/O bus. The IRQ controller asks the CPU permission to use the bus, to send

the byte to wherever. The IRQ controller reports back to the keyboard controller, giving clearance to send

the next character (byte):

A Guide to Adapters and I/O units.

The adapter or unit on the I/O bus uses the interrupt to signal request to send or receive data. An interrupt

signal is like a door bell. The unit signals by applying a voltage to one of the wires in the bus - an IRQ.

When the CPU acknowledges the signal, it knows that the unit wants send or receive data, or is finished.

The advantage of IRQ's is that the CPU can manage other tasks, while an adapter "massages" its data.

When the adapter has finished its task, it will report to the CPU with a new IRQ.

As an example, let us see how keyboard data are handled. The keyboard send bits, serially, through the

cable to the keyboard controller. The controller organizes them in groups of 8 (one byte). Every time it has a

byte, it sends an IRQ to the I/O bus. The IRQ controller asks the CPU permission to use the bus, to send

the byte to wherever. The IRQ controller reports back to the keyboard controller, giving clearance to send

the next character (byte):

A Guide to Adapters and I/O units.

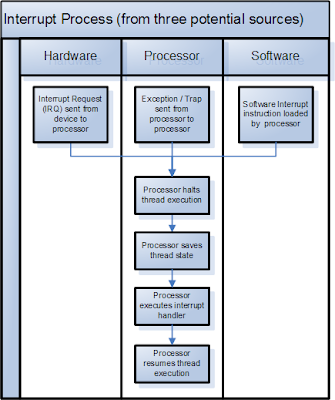

A hardware interrupt is an electronic alerting signal sent to the processor from an external device, either a part of the computer itself such as a disk controller or an externalperipheral. For example, pressing a key on the keyboard or moving the mouse triggers hardware interrupts that cause the processor to read the keystroke or mouse position. Unlike the software type (below), hardware interrupts are asynchronous and can occur in the middle of instruction execution, requiring additional care in programming. The act of initiating a hardware interrupt is referred to as an interrupt request (IRQ).

A software interrupt is caused either by an exceptional condition in the processor itself, or a special instruction in the instruction set which causes an interrupt when it is executed. The former is often called a trap or exception and is used for errors or events occurring during program execution that are exceptional enough that they cannot be handled within the program itself. For example, if the processor's arithmetic logic unit is commanded to divide a number by zero, this impossible demand will cause a divide-by-zero exception, perhaps causing the computer to abandon the calculation or display an error message. Software interrupt instructions function similarly to subroutine calls and are used for a variety of purposes, such as to request services from low level system software such as device drivers. For example, computers often use software interrupt instructions to communicate with the disk controller to request data be read or written to the disk.

Each interrupt has its own interrupt handler. The number of hardware interrupts is limited by the number of interrupt request (IRQ) lines to the processor, but there may be hundreds of different software interrupts.

Overview

Hardware interrupts were introduced as a way to reduce wasting the processor's valuable time in polling loops, waiting for external events. They may be implemented in hardware as a distinct system with control lines, or they may be integrated into the memory subsystem.

If implemented in hardware, an interrupt controller circuit such as the IBM PC's Programmable Interrupt Controller (PIC) may be connected between the interrupting device and the processor's interrupt pin to multiplex several sources of interrupt onto the one or two CPU lines typically available. If implemented as part of the memory controller, interrupts are mapped into the system's memory address space.

Interrupts can be categorized into these different types:

- Maskable interrupt (IRQ): a hardware interrupt that may be ignored by setting a bit in an interrupt mask register's (IMR) bit-mask.

- Non-maskable interrupt (NMI): a hardware interrupt that lacks an associated bit-mask, so that it can never be ignored. NMIs are used for the highest priority tasks such as timers, especially watchdog timers.

- Inter-processor interrupt (IPI): a special case of interrupt that is generated by one processor to interrupt another processor in a multiprocessor system.

- Software interrupt: an interrupt generated within a processor by executing an instruction. Software interrupts are often used to implement system calls because they result in a subroutine call with a CPU ring level change.

- Spurious interrupt: a hardware interrupt that is unwanted. They are typically generated by system conditions such as electrical interference on an interrupt line or through incorrectly designed hardware.

Processors typically have an internal interrupt mask which allows software to ignore all external hardware interrupts while it is set. Setting or clearing this mask may be faster than accessing an interrupt mask register (IMR) in a PIC or disabling interrupts in the device itself. In some cases, such as the x86 architecture, disabling and enabling interrupts on the processor itself act as a memory barrier; however, it may actually be slower.

An interrupt that leaves the machine in a well-defined state is called a precise interrupt. Such an interrupt has four properties:

- The Program Counter (PC) is saved in a known place.

- All instructions before the one pointed to by the PC have fully executed.

- No instruction beyond the one pointed to by the PC has been executed (that is no prohibition on instruction beyond that in PC, it is just that any changes they make to registers or memory must be undone before the interrupt happens).

- The execution state of the instruction pointed to by the PC is known.

An interrupt that does not meet these requirements is called an imprecise interrupt.

No comments:

Post a Comment